Vishay | 先进封装技术,如何赋能高功率密度 MOSFET 设计?两个案例告诉你~~

在今天的功率电子系统中,MOSFET 承载的电流和功率越来越大,而产品的尺寸却越来越紧凑,这就使得功率密度成为功率 MOSFET 选型时一个需要重点考量的指标。

想要提升 MOSFET 的功率密度,在前道工艺中采用先进的材料和制程,不断降低器件的导通和开关损耗,无疑是一条有效的技术路径;与此同时,在后道工艺中通过先进的封装技术,实现高效的热管理,有利于简化散热系统设计,降低 PCB 和相邻元器件的温度,减少系统的热应力,在进一步优化功率密度上也发挥着重要的作用。

因此,将高能效的器件设计与先进的封装技术相结合,已经成为今天功率 MOSFET 产品迭代升级的大趋势。这一趋势,在 Vishay 新一代功率 MOSFET 上体现得淋漓尽致。

比如,Vishay 推出的 SiSD5300DN 新型 30 V N 沟道 TrenchFET® 第五代功率 MOSFET,10 V 栅极电压条件下导通电阻仅为 0.71 mΩ,导通电阻与栅极电荷乘积,即开关应用中 MOSFET 关键的优值系数 ( FOM ) 为 42 mΩ*nC,在业界同类产品中也是出类拔萃。

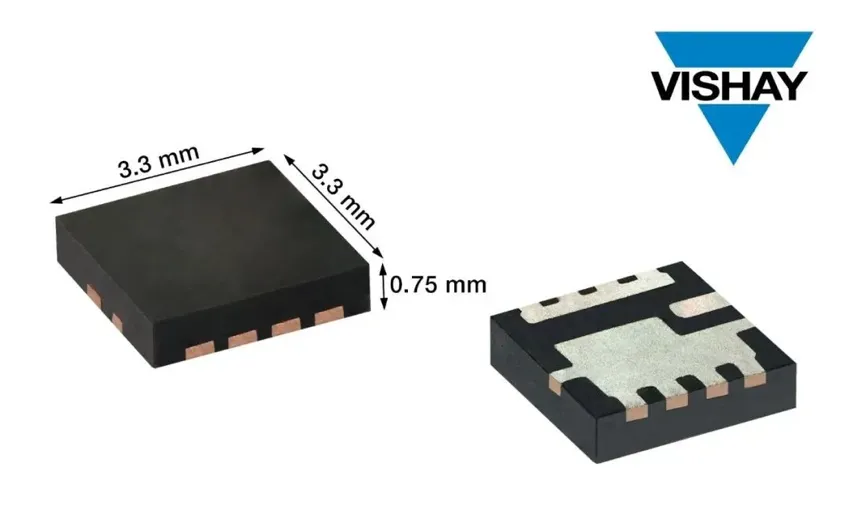

图 1:PowerPAK 1212-F 封装 SiSD5300DN 30 V N 沟道 MOSFET

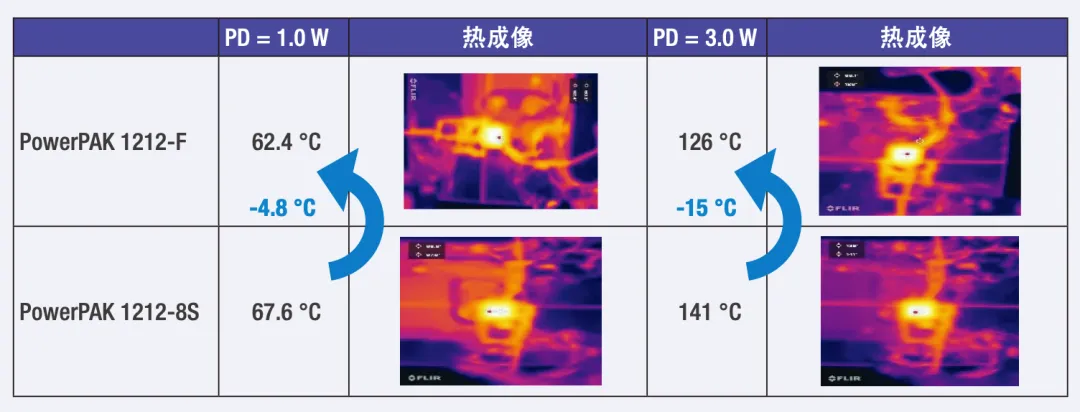

同时,SiSD5300DN 采用了基于源极倒装技术的 PowerPAK®1212-F 封装,与上一代 MOSFET 采用的 PowerPAK 1212-8S 封装相比,热阻从 63 °C/W 降至 56 °C/W,源极焊盘尺寸增加了 10 倍 ( 从 0.36 mm2 提高到 4.13 mm2 ),大大改善了热性能。从下图中可以看到,采用 PowerPAK 1212-F 封装的 SiSD5300DN 在恒定功率条件对比测试中,处理相同电流时的工作温度明显降低。

图 2:采用 PowerPAK 1212-F 封装的 SiSD5300DN

具有更好的热性能

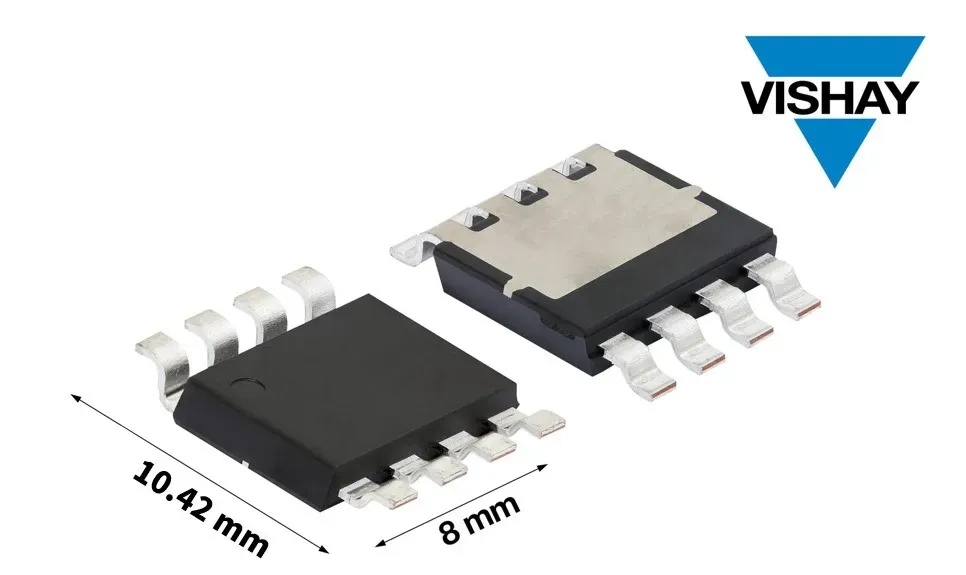

基于新型 PowerPAK® 8 x 8 LR 封装的第四代 600 V E 系列功率 MOSFET,是另一个成功的范例。与前代器件相比,其导通电阻降低了 27 %,导通电阻与栅极电荷乘积 (即RDS(on)x Qg FOM) 下降了 60 %。

图3:基于新型 PowerPAK® 8 x 8 LR 封装的

第四代 600 V E 系列功率 MOSFET

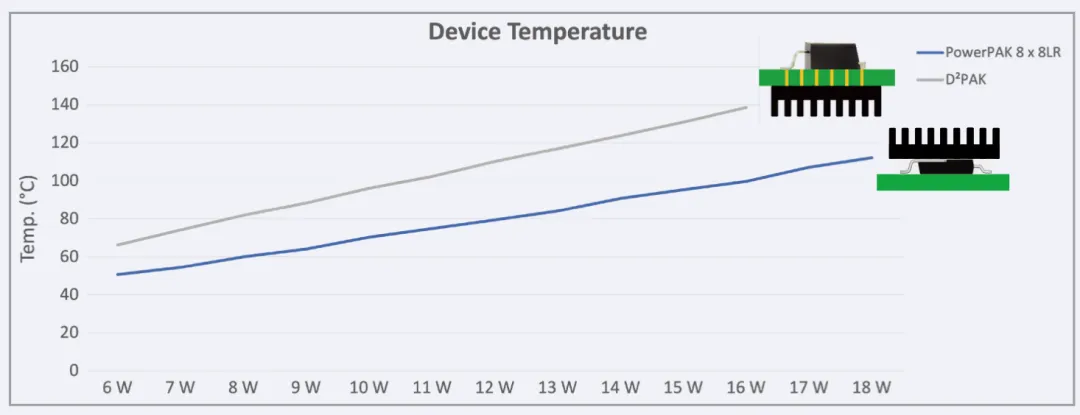

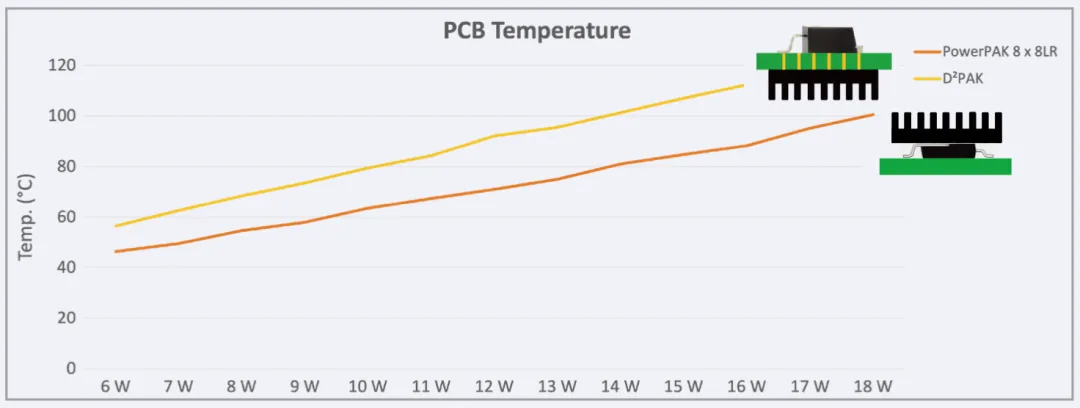

特别值得一提的是,由于该功率 MOSFET 采用了独特的顶侧冷却封装解决方案,与采用底侧冷却的 D2PAK 封装相比,占位面积节省 52.4 %,高度降低 66 %,结壳(漏极)热阻 R thjc 仅为 0.25 °C/W,在相同导通电阻下额定电流增加 45 %,从而显著提高可额定功率和功率密度,这使其成为 3 kW 以下电源解决方案的理想选择。

图4:新型顶侧冷却 PowerPAK® 8 x 8 LR 封装与传统的

底侧冷却 D2PAK 封装相比,具有更佳的热性能,

在相同功率下具有更低的器件和 PCB 温度。

在功率电子系统的设计中,具有更高功率密度的 MOSFET 可以带来更高的能效、热效率、电流输出,以及板级可靠性。Vishay 将先进的封装技术与创新的器件设计相结合,打造出了具有出色高功率密度的、品类丰富的功率 MOSFET 产品。

上文提到的两款产品,就是其中的代表作。