碳化硅赋能浪潮教程:利用 SiC CJFET替代超结 MOSFET

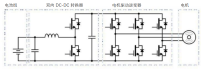

碳化硅(SiC)凭借其优异的材料特性,在服务器、工业电源等关键领域掀起技术变革浪潮。本教程聚焦 SiC 尤其是 SiC JFET 系列器件,从碳化硅如何重构电源设计逻辑出发,剖析其在工业与服务器电源场景的应用价值。 本文将介绍利用 SiC CJFET替代超结 MOSFET以及开关电源应用。 利用 SiC CJFET替代超结 MOSFET

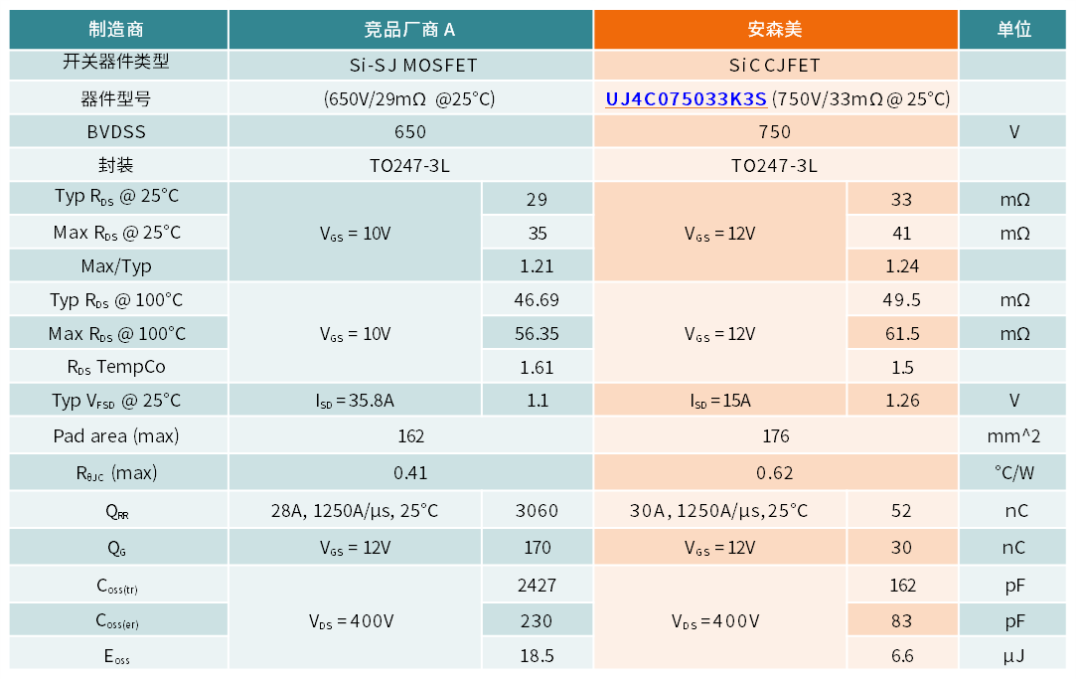

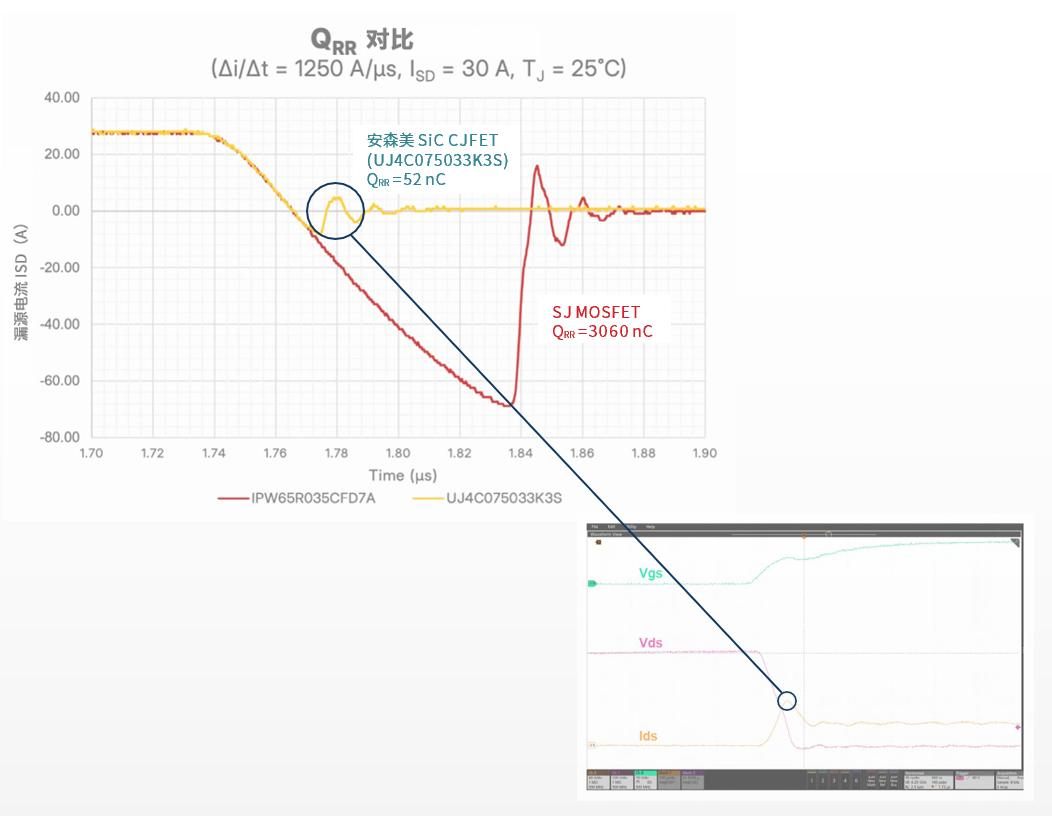

本表对比了安森美(onsemi) EliteSiC CJFET 器件 UJ4C075033K3S 与某竞品厂商的Si超结(SJ) MOSFET 的关键特性。其中,UJ4C075033K3S 在25°C 下的额定值为 750 V,33 mΩ; 而竞品Si SJ MOSFET 在25°C 下的额定值为 650 V,29 mΩ。在此对比中,该 CJFET 的反向恢复电荷 QRR 降低至 1/60,栅极电荷 QG 降低至 1/6,反向传输电容 COSS(tr) 降低至 1/10。

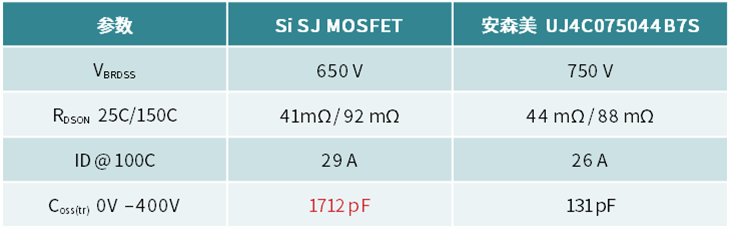

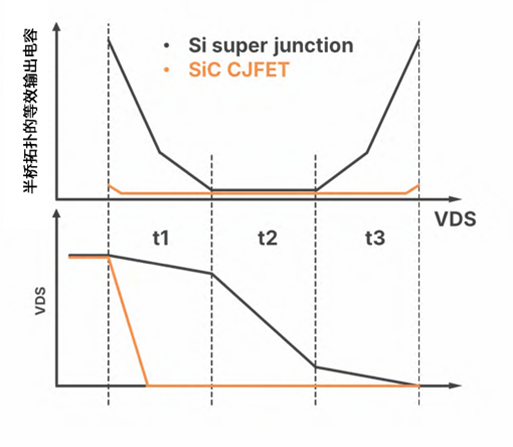

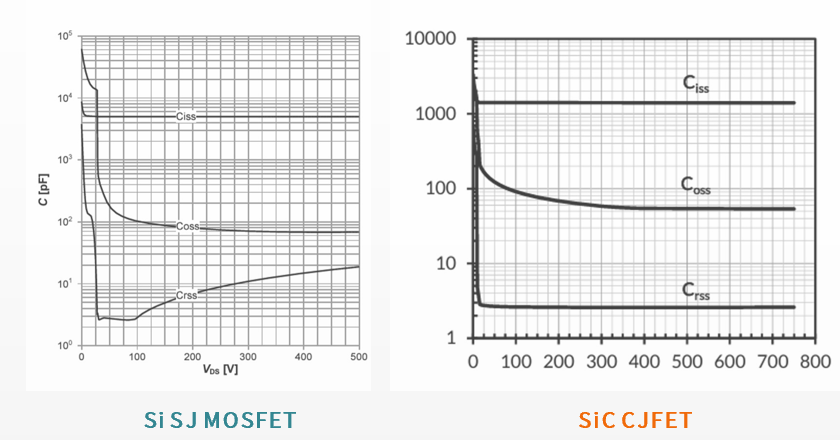

SiC CJFET 与 Si SJ MOSFET 之间最显著的差异在于电容特性与裸片尺寸。在安森美 UJ4C075044B7S CJFET 与某竞品 Si SJ MOSFET 的对比中,尽管 CJFET 的阻断电压 VBRDSS 高出 100V,且两者的导通电阻 RDS(on) 额定值相近,但 SJ MOSFET 的反向传输电容 COSS(tr) 却高出 13倍 以上。这一差异源于 SJ MOSFET在低压范围内表现出的非线性特性,如下图所示。CJFET 的电压转换时间远短于SJ MOSFET 。在采用半桥整流拓扑(而非全桥)的电源系统中,CJFET 能始终实现显著更快的开关速度。

在用 SiC CJFET替代 Si SJ MOSFET 时,安森美建议通过调整死区时间(dead time)或在 CJFET 上增加缓冲电容,以有效管理因死区引起的导通损耗。尤其在较高开关频率下,死区时间带来的影响会变得更加显著。

对于CJFET而言,从检测到电流反向到JFET沟道完全导通通常存在延迟。举例来说:若死区时间为 100 ns,而开关频率为 100 kHz,则开关周期为 10 µs,此时死区仅占周期的 1%,该延迟影响相对较小。然而,若开关频率提升至 1 MHz,开关周期将缩短至 1 µs,死区时间便占整个周期的 10%,其影响不可忽视。

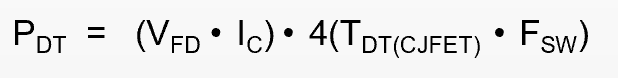

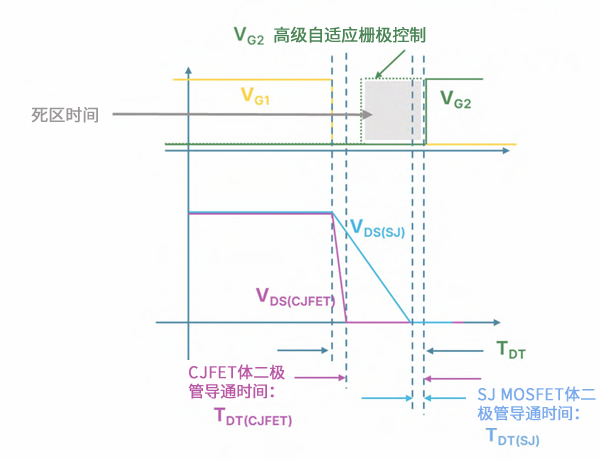

在相同死区时间下,相较于 Si SJ MOSFET,SiC CJFET 的漏源电压 VDS 放电速度更快,导致其体二极管在剩余死区时间内持续导通。假设 CJFET 剩余死区时间 TDT(CJFET) 为 0.2 µs,体二极管正向压降 VFD 为 1.2 V,开关频率 FSW 为 100 kHz,开关电流 IC 为 10 A,则全桥拓扑中由剩余死区引起的功率损耗 PDT 可通过以下公式计算:

在此案例中,计算得出的损耗为0.96W。然而,通过对栅极应用Adaptive Gate Control, 在死区时间内提前提升 VG2,让 VDS(CJFET) 降至 0V 的瞬间开通。即可使该部分损耗趋近于零。这一效果可通过观测 VDS 与 VGS 的输出波形加以验证。

死区时间越长,体二极管导通损耗的持续时间也越长。通过缩短 CJFET 的死区时间,或为其增加缓冲电容以匹配 Si SJ MOSFET 的 COSS ,可有效改善此问题。

在对比 SiC CJFET与Si SJ MOSFET时,当两者具有相同的电流变化率( Δi/Δt )并在相同的结温( TJ = 25°C )下工作,安森美UJ4C075033K3S CJFET 的反向恢复电荷( QRR )最多可比后者低 60 倍 。更小的反向恢复电荷意味着更高效率、更低噪声与更优的电磁兼容性。此外,CJFET在反向恢复过程中没有导致器件失效的风险,可显著提升系统整体稳健性。

开关电源应用

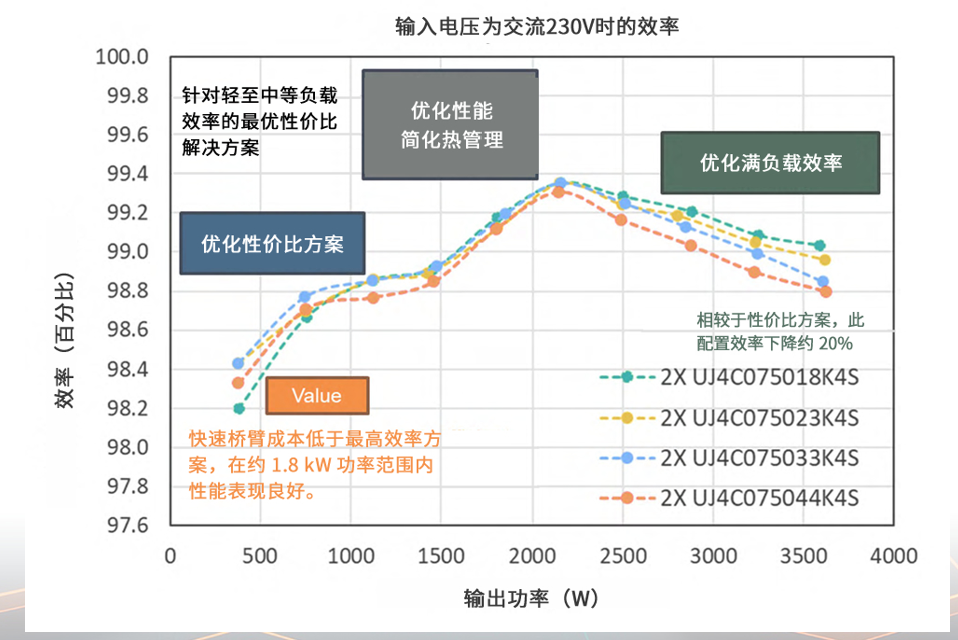

为展示CJFET在电源快速开关需求下的性能,我们测试了四款不同的安森美 CJFET 器件在3.6 kW图腾柱功率因数校正 (TPPFC) 硬开关拓扑中的效率。所有被测CJFET在半负载条件下均实现了超过99% 的峰值效率。

同步整流的实现,首先在于用可控的场效应晶体管(FET)替代谐振型电源转换器中通常在初级侧(有时也在次级侧)使用的二极管。由于这些 FET 的开关时序可以更直接地控制,转换器输出的直流波形能够更准确地匹配负载所需的电压和频率。

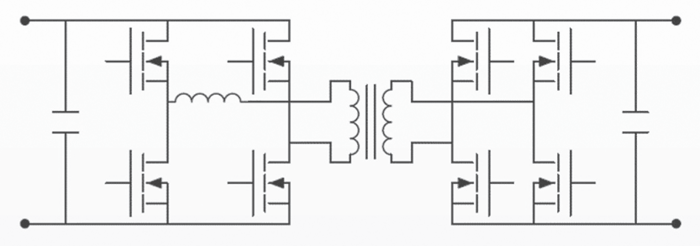

全桥移相有源桥零电压转换拓扑

以这种在 AC-DC 应用中日益普及的电路拓扑为例:所有通常使用二极管的开关位置均被场效应晶体管替代。“ZVT”代表零电压转换,该技术巧妙利用了主变压器的漏电感与开关的输出电容——这些通常被视为寄生元件的特性——并将其转化为优势。

例如,在标准全桥拓扑中置于初级侧外部的漏电感,现在可集成至内部。它在实现相同功能的同时,大幅缩减了占用空间。

通过有源桥移相控制,脉宽调制(PWM)可转换为固定开关频率的工作模式,这使控制实现更为简便,同时降低了开关对击穿电压的耐压要求。电磁干扰频谱也更为集中,使系统在整个宽输出电压范围内均能实现稳定且高效率的运行。

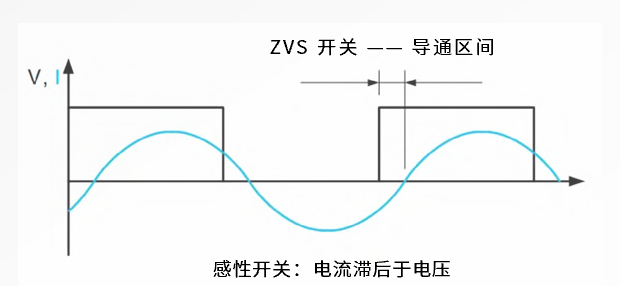

从电气工程师的角度来看,全桥功率转换过程的一大优势在于它能够实现软开关。严格来说,ZVS 并非一种刻意设计的技术手段,而更像是一种可被巧妙利用的物理现象。它通过功率转换器的谐振网络(或称“谐振腔”)得以实现。

典型的零电压开关会利用电容和电感构成一个谐振电路(即“谐振腔”)。而在实际应用中,常以变压器固有的励磁电流作为便捷的替代。可以把这个励磁电流看作一种振荡信号,它能够在PFC电路中 MOSFET(或 CJFET)两端电压为零(或极低)时,将器件导通。

波形整形的核心思想是:在输入电压处于波峰或波谷时导通或关断输出开关,而谐振所产生的自然振荡,恰好为这种基于电感特性的开关动作提供了理想时序。

该电流被有意设置为相位滞后于谐振网络的电压,正是这种滞后引发了谐振,从而触发场效应晶体管导通(并促使其他开关按序关断)。在此过程中,开关损耗得以有效避免,EMI 噪声也显著降低。

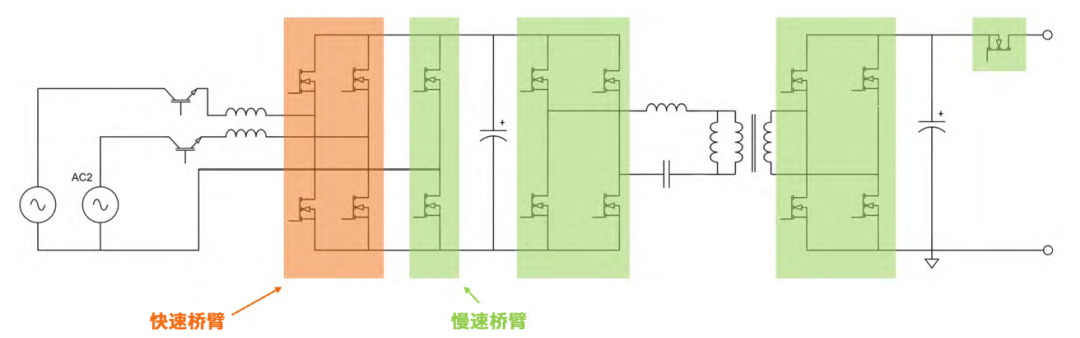

这是前文介绍的图腾柱PFC完整电路图。这种全"无桥式"拓扑结构包含五个功率转换级。最左侧为硬开关,其余四个均采用软开关技术。从左至右,每个同步整流转换级的电路结构逐级简化。

对于“快速桥臂”(即硬开关),图腾柱PFC需搭配RC缓冲器使用CJFET。若PCB布局空间受限无法容纳此元件,则 SiC MOSFET 可能成为唯一选择。否则,若考虑 CJFET 配合 RC 缓冲电路所能实现的性能特性,CJFET 将是更优方案。

对于"慢速桥臂"(即同步整流器件),其核心要求是具备低导通电阻RDS(on) ,因此CJFET是最佳选择。

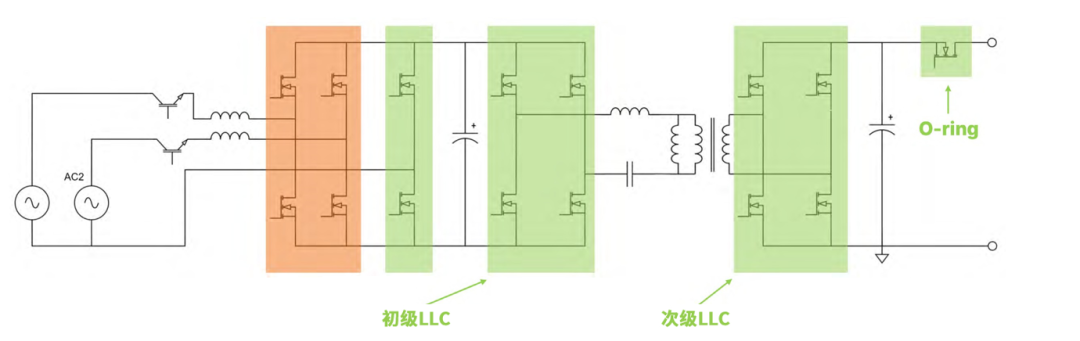

对于位于中间的初级 LLC 转换级(因其紧邻两个电感L和一个电容C而得名),导通损耗是主要损耗因素。在高开关频率下,关断开关损耗是另一个关键参数,因为 LLC 作为一种零电压开关(ZVS)拓扑,不存在导通损耗。CJFET 在配置缓冲器后已展现出极低的关断能量损耗Eoff ,因此是初级 LLC 转换级的最佳选择。

随后的次级 LLC 转换级以及最右侧的 O-Ring 级可用于 400 V 输出电压的设计中。对于此类高压应用,低导通电阻 RDS(on) 和低输出电容 COSS 至关重要,这使得 CJFET 在整个次级侧相比 SiC MOSFET 或 Si SJ MOSFET 更具优势。

未完待续,我们将介绍CJFET通常需要配置缓冲电路的原因等。

厦门唯样ONEYAC电子元器件平台,主营元器件代理,现货库存,自营仓储,厦门仓/香港仓直发,原厂官方授权,当天发货,渠道来源可追溯,快速BOM配单,阻容感国内领先优势,稳定交付。